(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

## ANALYSIS AND COMPARISON OF VARIOUS PULSE WIDTH MODULATION STRATEGIES FOR HYBRID INVERTER WITH REDUCED NUMBER OF COMPONENTS

#### \*N.Susheela, \*\*P.Satish Kumar,

\*Department of Electrical Engineering, University College of Engineering (A),Osmania University, Hyderabad, Telangana \*\*Department of Electrical Engineering, University College of Engineering (A),Osmania University, Hyderabad, Telangana

## ABSTRACT

Performance of hybrid inverter with less number of components is presented in this paper. When compared to diode clamped, flying capacitors, and cascaded H-bridge multilevel inverters, the hybrid inverter requires fewer components, fewer carrier signals and gate drives. Therefore, the overall cost and complexity are greatly reduced particularly as the output voltage level increases. Implementation of single phase seven-level, nine-level and eleven-level hybrid inverter have been performed using sinusoidal pulse width modulation (SPWM) techniques i.e., phase disposition (PD) and alternate phase opposition disposition (APOD). The total harmonic distortion (THD) is evaluated for various modulation indices using MATLAB/SIMULINK.

**Keywords:** sinusoidal pulse width modulation; hybrid inverter; alternate phase opposition disposition; phase disposition; total harmonic distortion;

## **INTRODUCTION**

The general concept of multilevel inverters involves utilizing a higher number of active semiconductor switches to perform the power conversion in small voltage steps. There are several advantages to this approach when compared with the conventional power conversion approach. The smaller voltage steps lead to the production of higher power quality waveforms and also reduce voltage (dv/dt) stress on the load. Another important feature of multilevel converters is that the semiconductors are wired in a series-type connection, which allows operation at higher voltages.

Multilevel inverters have attracted a great deal of attention in medium and high-power applications due to their lower switching losses. The most recently used inverter topologies, which are mainly addressed as applicable multilevel inverters, are Diode clamped or Neutral-point clamped (NPC) inverter, Flying Capacitor inverter, and Cascaded or H-bridge inverters. Hybrid inverter has

#### INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

http://www.ijiest.in

(IJIEST) 2017, Vol. No. 3, Jan-Dec

#### e-ISSN: 2454-9584; p-ISSN: 2454-8111

some advantages (particularly in higher levels) when compared with the above multilevel inverters. This topology eliminates entirely the diodes and capacitors used in diode clamped inverters [1], capacitors used in flying capacitor inverters [2] and reduces the number of switches and carrier signals than in the cascaded inverters [3], diode clamped, and flying capacitors inverters. Some new approaches have been recently suggested such as the topology utilizing low-switching-frequency high-power devices [4-5]. Although the topology has some modification to reduce output voltage distortion, the general disadvantage of this method is that it has significant low-order current harmonics. Another approach which requires different voltage source values which are defined according to the target selection [6]. However, this approach also needs basic units which are connected in series, and the basic units still require more switches than the proposed topology. Another disadvantage of this topology is that the power switches and diodes also need to have a different rating which is a major drawback of the topology. Voltage sources are not used efficiently in generating output voltage levels [7-8]. For example, it can generate only five output levels with four dc sources, while conventional multilevel inverters can generate up to nine levels with the same number of power supplies.

The proposed topology is a symmetrical topology since all the values of all voltage sources are equal. However, there are asymmetrical topologies [9] which require different voltage sources. This criterion needs to arrange dc power supplies according to a specific relation between the supplies. Difference in ratings of the switches in the topology is also a major drawback of the topology. This problem also happens in similar topologies [10-12], while some of the high-frequency switches should approximately withstand the maximum overall voltage which makes its application limited for high-voltage products. Some of the proposed topologies suffer from complexities of capacitor balancing [13-15]. In [16], the capacitor values used in the topology are proportional to the load current, and as the load current increases, a larger capacitor should be selected. In [14], the capacitor voltage will affect the output voltage when modulation index reaches near its extreme values, i.e., zero or one.

The hybrid inverter topology has advantages when compared with the above mentioned topologies. It has less number of switches, less number of carrier waves and has the component which operates the switching devices at line frequency that results in more efficiency. Therefore, there is no need for all switches to work in high frequency which leads to simpler and more reliable control of the inverter. In this topology general modulation technique i.e., phase disposition and alternate phase opposition disposition sinusoidal pulse width modulation is utilized to drive the inverter.

### SINUSOIDAL PULSE WIDTH MODULATION TECHNIQUES

Mainly the power electronic converters are operated in the "switched mode", which means the switches within the converter are always in either one of the two states - turned off (no current flows), or turned on (saturated with only a small voltage drop across the switch). To control the flow of power in the converter, the switches alternate between these two states (i.e. on and off). This happens rapidly enough that the inductors and capacitors at the input and output nodes of the converter average or filter the switched signal. The switched component is attenuated and the desired DC or low frequency AC

http://www.ijiest.in

(IJIEST) 2017, Vol. No. 3, Jan-Dec

component is retained. This process is called pulse width modulation (PWM), since the desired average value is controlled by modulating the width of the pulses [16].

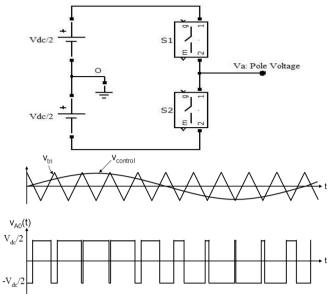

The fundamental methods of pulse-width modulation (PWM) are divided into the traditional voltage-source and current-regulated methods. A sample PWM method is shown in Fig.1.

Figure 1. Sinusoidal pulse-width modulation(SPWM).

Inverter output voltage is

$$V_{A0} = \frac{V_{dc}}{2}, \text{ When } v_{\text{control}} > v_{\text{tri}}$$

(1)

$$V_{A0} = -\frac{V_{dc}}{2}, \text{ When } v_{\text{control}} < v_{\text{tri}}$$

(2)

PWM frequency is the same as the frequency of  $v_{tri}$ . Amplitude is controlled by the peak value of v<sub>control</sub> and Fundamental frequency is controlled by the frequency of v<sub>control</sub>. Mo )

odulation Index (m) is given by:

$$m = \frac{V_{control}}{V_{tri}}$$

(3)

The modulation techniques of SPWM used are phase disposition (PD) and alternate phase opposition disposition (APOD)SPWM.

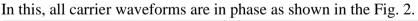

#### A. Phase Disposition (PD) SPWM

http://www.ijiest.in

(IJIEST) 2017, Vol. No. 3, Jan-Dec

#### e-ISSN: 2454-9584; p-ISSN: 2454-8111

#### B. Alternate Phase Opposition Disposition (APOD)SPWM

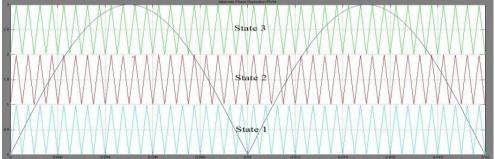

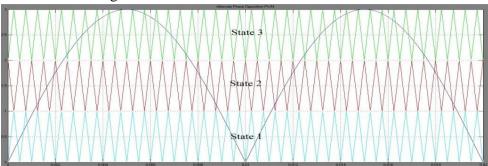

In this modulation, every carrier waveform is in out of phase with its neighbor carrier by  $180^{0}$  as seen in Fig.3.

Figure 3. Alternate phase opposition disposition for seven level hybrid inverter.

### **HYBRID INVERTER**

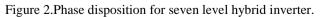

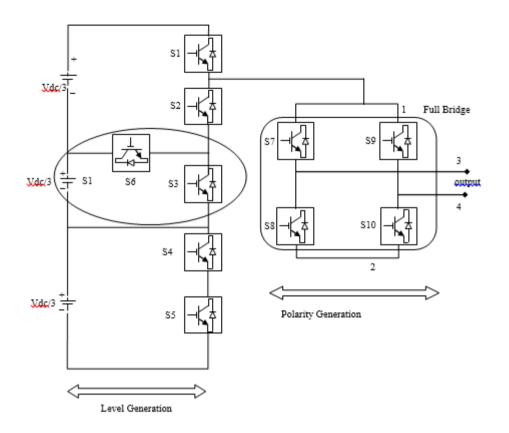

The hybrid multilevel inverter is a combination of level generation as well as polarity generation parts which is responsible for multilevel output voltage generation. Here, the level generation part that consists of high-frequency switches produce the positive levels. And the polarity generation part with low frequency switches is responsible to give output polarity[17]. Hybrid MLI mainly eliminates higher number switches that are required to produce output levels. The structure of single phase hybrid inverter for seven levels is shown in Fig.1 which needs only 3 isolated sources and 10 switches. The required output levels without polarity are produced by high frequency switches. Whereas, the polarity of output voltage is decided by the switches that has low frequency. Just by duplicating the state that is represented in the middle of Fig.4, it can be applied to any number of voltage levels. The classical seven level MLI using SPWM requires six carriers, but three carriers are needed for hybrid MLI.

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Figure 4.Seven level hybrid multilevel inverter structure.

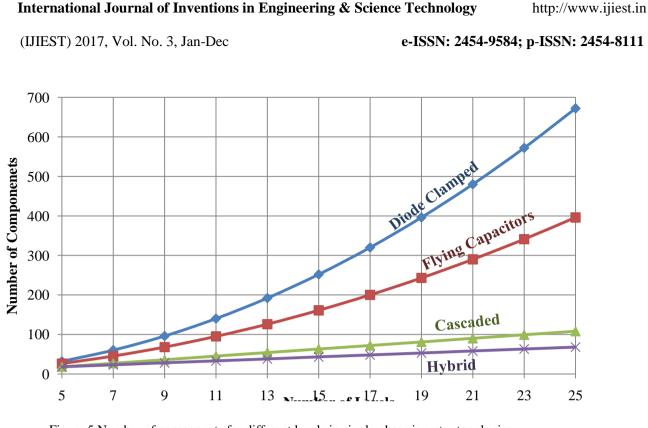

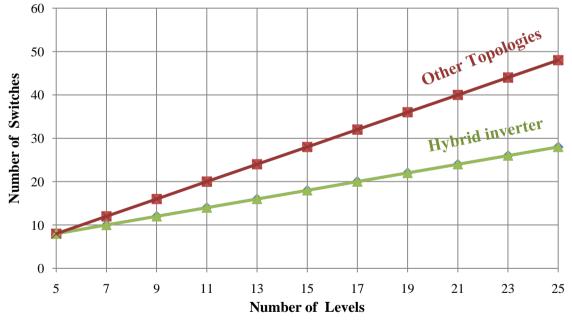

The number of components required for single-phase hybrid inverter are lower than that of other topologies. The hybrid inverter requires fewer components and also fewer switches compared to others. Therefore, it should have the potential of finding widespread applications in high-voltage power devices and apparatus that includes FACTS, HVDC, etc.

As the most important part in multilevel inverters is the power semiconductor switches which define the reliability and control complexity, the number of required components and switches against the required voltage levels is shown in Fig. 5 and Fig.6 for the hybrid inverter as well as conventional topologies.

Figure 5.Number of components for different levels in single phase inverter topologies.

#### Figure 6.Number of switches for different levels in single phase inverter topologies.

### **RESULTS AND DISCUSSION**

The following are the results which are simulated using MATLAB/Simulink for single-phase hybrid inverter. The waveforms are shown below for different levels.

INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

http://www.ijiest.in

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

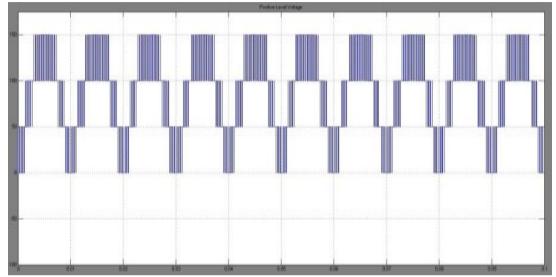

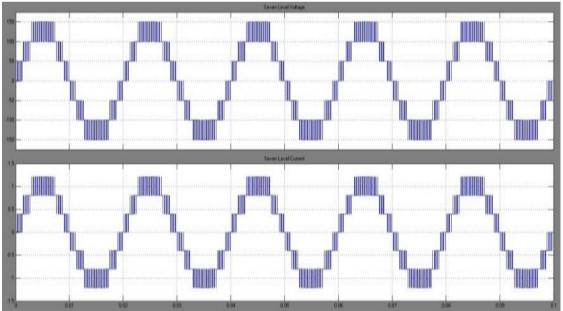

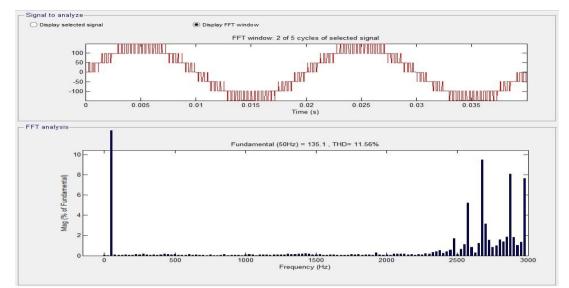

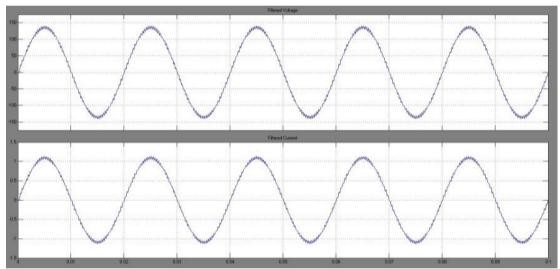

### A. Results of Seven-Level Hybrid Inverter

The waveforms obtained for seven level hybrid inverter are presented from Fig. 7 to Fig.13.

Figure 7.Output voltage of level generation part for seven level inverter with R load.

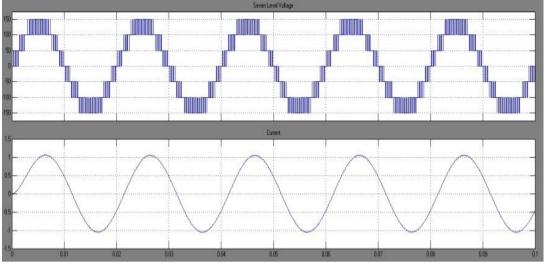

The positive levels which are generated by level generation part as shown above is converted into required seven level output by using the polarity generation part by changing the polarity of second half cycle of every full cycle which is as shown below.

Figure 8.Voltage and current of seven level inverter with R load.

# INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

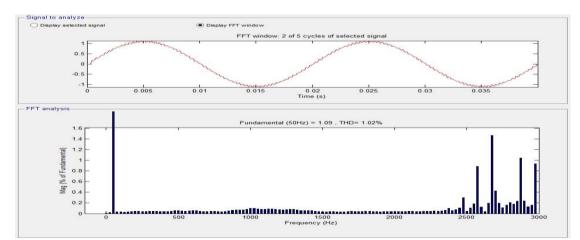

Figure 9.FFT analysis of voltage for seven level inverter with Rload.

Figure 10. Voltage and current of seven level inverter for Rload with LC filter.

Figure 11.FFT Analysis of seven level inverter current for Rload with LC Filter.

## INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Figure 12.Voltage and current of seven level inverter with RL load.

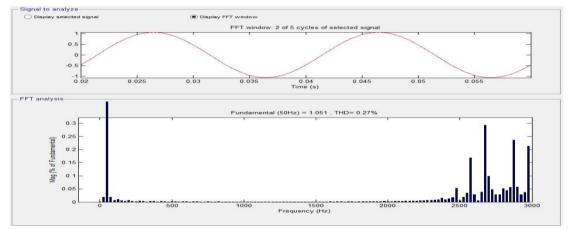

Figure 13. FFT analysis of seven level inverter current for RL load.

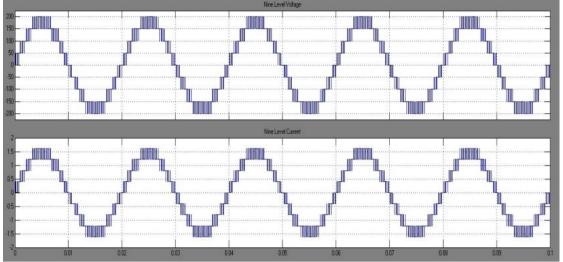

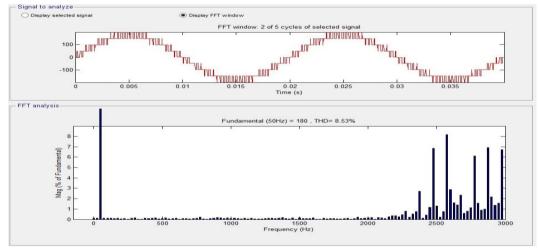

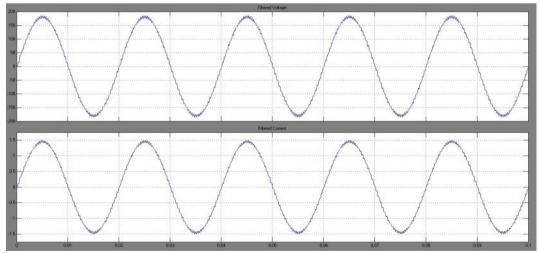

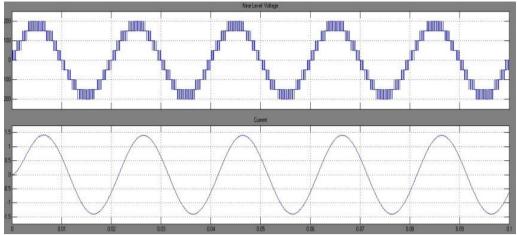

### B. Results of Nine-Level Hybrid Inverter

Fig. 14to Fig.18 shows the results for nine level hybrid inverter.

Figure 14.Output voltage of level generation part for nine level inverter with R load.

## INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Figure 15.Voltage and current of nine level inverter with R load.

Figure 16.FFT analysis of nine level inverter voltage for R load.

Figure 17.Voltage and currents of nine level inverter using Rload with LC filter.

## INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Figure 18. Voltage and current of nine level inverter with RL load.

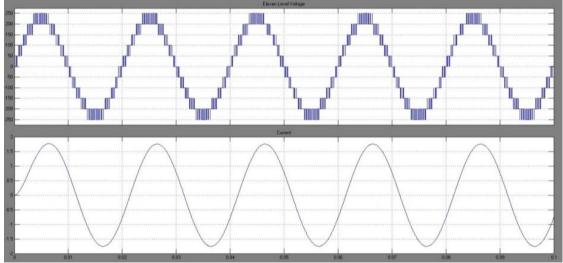

#### C. Results of Eleven-Level Hybrid Inverter

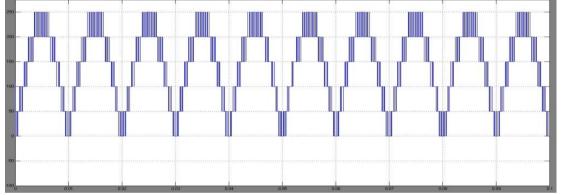

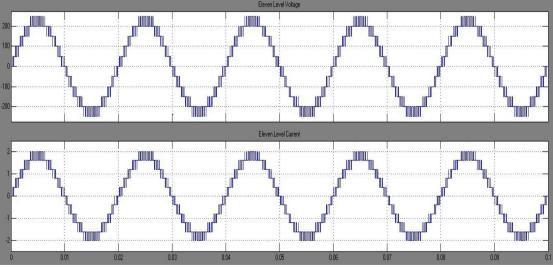

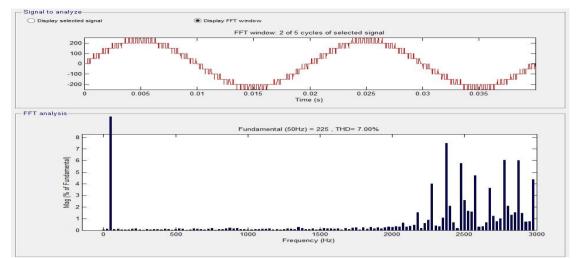

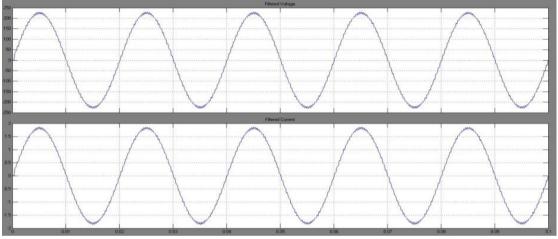

The waveforms obtained for eleven level hybrid inverter are presented from Fig. 19 to Fig.23.

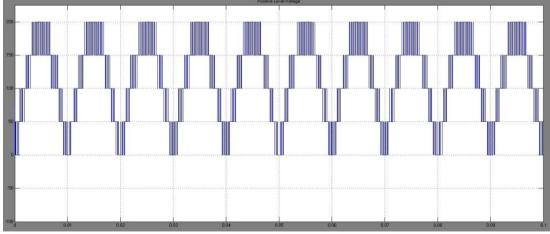

Figure 19. Output voltage of level generation part for eleven level inverter with R load.

Figure 20.Voltage and currents of eleven level inverter with R load.

## INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Figure 21. FFT analysis of eleven level inverter voltage with Rload.

Figure 22. Voltage and current of eleven level inverter for R load with LC filter.

Figure 23.Voltage and currents of eleven level inverter for RL load.

## INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

http://www.ijiest.in

(IJIEST) 2017, Vol. No. 3, Jan-Dec

e-ISSN: 2454-9584; p-ISSN: 2454-8111

Comparison of THD for various modulation indices using phase disposition and alternate phase opposition disposition sinusoidal pulse width modulation techniques for different levels are tabulated below in tables I and II.

| No. of<br>Levels | $M_a$ | PD      | APOD        |                |                 |  |

|------------------|-------|---------|-------------|----------------|-----------------|--|

|                  |       | Without | With Filter | Without Filter | ter With Filter |  |

|                  |       | Filter  |             |                |                 |  |

|                  | 0.85  | 12.29   | 1.13        | 12.21          | 1.10            |  |

| _                | 0.9   | 11.48   | 1.05        | 11.56          | 1.02            |  |

| 7<br>9           | 0.95  | 11.08   | 1.00        | 11.12          | 0.99            |  |

|                  | 1     | 9.84    | 0.92        | 9.70           | 0.86            |  |

|                  | 0.85  | 9.05    | 0.81        | 8.96           | 0.78            |  |

|                  | 0.9   | 8.60    | 0.92        | 8.53           | 0.83            |  |

|                  | 0.95  | 8.40    | 0.84        | 8.37           | 0.74            |  |

|                  | 1     | 7.38    | 0.81        | 7.44           | 0.69            |  |

| 11               | 0.85  | 7.17    | 0.79        | 7.34           | 0.72            |  |

|                  | 0.9   | 6.78    | 0.8         | 7.00           | 0.71            |  |

|                  | 0.95  | 6.58    | 0.83        | 6.52           | 0.71            |  |

| _                | 1     | 6.09    | 0.77        | 6.02           | 0.66            |  |

Table II.

Current THD (%) for Single Phase Hybrid Inverter with RL-Load

|      | 7-Level |      | 9-Level |      | 11-Level |      |

|------|---------|------|---------|------|----------|------|

| Ma   | APOD    | PD   | APOD    | PD   | APOD     | PD   |

| 0.85 | 0.28    | 0.28 | 0.20    | 0.21 | 0.16     | 0.17 |

| 0.9  | 0.27    | 0.26 | 0.20    | 0.20 | 0.16     | 0.17 |

| 0.95 | 0.24    | 0.25 | 0.18    | 0.19 | 0.15     | 0.16 |

| 1    | 0.22    | 0.22 | 0.16    | 0.17 | 0.14     | 0.14 |

## CONCLUSION

In this paper, hybrid inverter has been implemented which has superior features over diode clamped inverter, cascaded inverter, and flying capacitor etc., in terms of the required power switches, control requirements, cost and reliability. The efficiency is improved and the converter size and cost of the system are greatly reduced. The single-phase results of the hybrid inverter at various modulation indices for seven-level, nine-level and eleven-level are presented at different loads .The results clearly shows that, the proposed topology can effectively work with reduced number of switches and carriers for SPWM which results in low THD.

#### INTERNATIONAL JOURNAL OF INVENTIONS IN ENGINEERING AND SCIENCE TECHNOLOGY

(IJIEST) 2017, Vol. No. 3, Jan-Dec

#### e-ISSN: 2454-9584; p-ISSN: 2454-8111

### ACKNOWLEDGMENT

We thank the Science and Engineering Research Board (SERB), Government of India, New Delhi for providing Research Project under 'Fast Track Scheme for Young Scientists' to carry out the Research on Multilevel Inverters. We also thank Principal and Head, Department of Electrical Engineering, University College of Engineering (Autonomous), Osmania University, Hyderabad.

## REFERENCES

- [1] Xiaoming Yuanand Ivo Barb, "Fundamentals of a New Diode Clamping Multilevel Inverter", IEEE Transactions on Power Electronics, Vol.15, No.4, July 2000.

- <sup>[2]</sup> Jih-Sheng Lai, IEEE, and Fang ZhengPeng, "A New Breed of flying Capacitor Multilevel Converter" IEEE Transactions On Industry Applications, VOL. 32, NO. 3, MAYIJUNE 1996

- [3] Yun XU, Yunping ZOU, Xiong LIU, Yingjie He, "A Novel Composite Cascade Multilevel Converter", IEEE Industrial Electronics Society (IECON), Nov. 5-8, 2007.

- [4] G. M. Martins, J. A. Pomilio, S. Buso, and G. Spiazzi, "Three-phase low frequency commutation inverter for renewable energy systems," IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 1522–1528, Oct. 2006.

- [5] N.Susheela, P.Satish Kumar and C.H.Reddy, "Performance Analysis of Four Level NPC and NNPC Inverters using Capacitor Voltage Balancing Method" IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), pp. 212-217, Dec 2016,doi:10.1109/UPCON.2016.7894654.

- [6] G. S. Perantzakis, F. H. Xepapas, and S. N. Manias, "A novel four-level voltage source inverterinfluence of switching strategies on the distribution of power losses," IEEE Trans. Power Electron., vol. 22, no. 1, pp. 149–159, Jan. 2007.

- [7] G. Mondal, K. Gopakumar, P. N. Tekwani, and E. Levi, "A reducedswitch- count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive," IEEE Trans. Ind. Electron., vol. 54, no. 4, pp. 2344–2351, Aug. 2007.

- [8] N.Susheela, P.Satish Kumar and S.K.Sharma, "Mapping Method Based Space Vector Modulation Technique for Diode Clamped Multilevel Inverters" IEEE Uttar Pradesh Section International Conference on Electrical, Computer and Electronics Engineering (UPCON), pp. 410-415, Dec 2016. doi:10.1109/UPCON.2016.7894689.

- [9] S. G. Song, F. S. Kang, and S.J. Park, "Cascaded multilevel inverteremploying three-phase transformers and single dc input," IEEE Trans.Ind. Electron., vol. 56, no. 6, pp. 2005–2014, Jun. 2009.

- [10] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and M. I. Gimenez, "A new simplified multilevel inverter topology for dc-ac conversion," IEEE Trans. Power Electron., vol. 21, no. 5, pp. 1311–1319, Sep. 2006.

(IJIEST) 2017, Vol. No. 3, Jan-Dec

#### e-ISSN: 2454-9584; p-ISSN: 2454-8111

- [11] N. A. Rahim, K. Chaniago, and J. Selvaraj, "Single-phase seven-level grid-connected inverter for photovoltaic system," IEEE Trans. Ind. Electron., vol. 58, no. 6, pp. 2435–2443, Jun. 2011.

- [12] J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital PI controller", IEEE Trans. Ind. Electron., vol. 56, no. 1, pp. 149–158, Jan. 2009.

- [13] S. A. Gonzalez, M. I. Valla, and C. F. Christiansen, "Analysis of a cascade asymmetric topology formultilevel converters", in Proc. IEEE ISIE, pp. 1027–1032, 2007.

- [14] P. Lezana and J. Rodriguez, "Mixed multicell cascaded multilevel inverter", in Proc. IEEE ISIE, pp. 509–514, 2007.

- [15] N.Susheela, P.Satish Kumar, B.Sirisha, "Hybrid Topologies of Multilevel Converter for Current Waveform Improvement", International Journal of Inventive Engineering and Sciences (IJIES), ISSN: 2319–9598, Volume-1, Issue-4, pp.29-37, March, 2013.

- [16] N. Mohan, T. M. Undeland, and W. P. Robbins, Power Electronics: Converters, Applications, and Design, Second Edition, John Wiley and Sons, 1995.

- <sup>[17]</sup> EhsanNajafi, and Abdul Halim Mohamed Yatim, "Design and Implementation of a New Multilevel Inverter Topology", IEEE Transactions on Industrial Electronics, Vol. 59, No. 11, November 2012.